Serving tech enthusiasts for over 25 years.

TechSpot means tech analysis and advice you can trust.

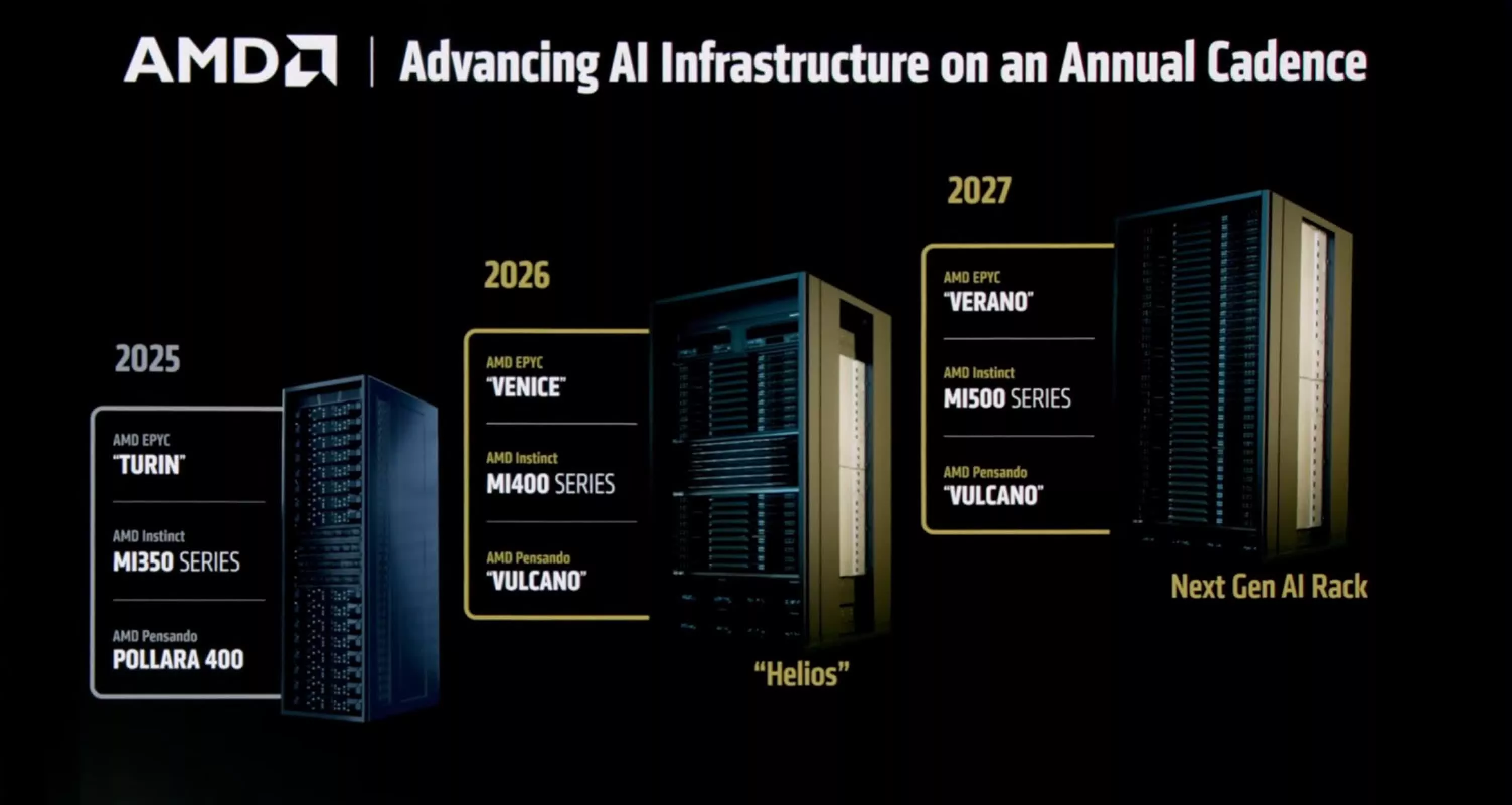

What just happened? AMD is preparing to shake up the data center landscape with its forthcoming Epyc Venice processor, a chip that promises to set new standards for performance and scalability in server computing. Announced at the company's recent Advancing AI event, the Venice CPU is built on AMD's next-generation Zen 6 architecture and is slated for release in 2026, targeting the ever-increasing demands of artificial intelligence, cloud computing, and high-performance analytics.

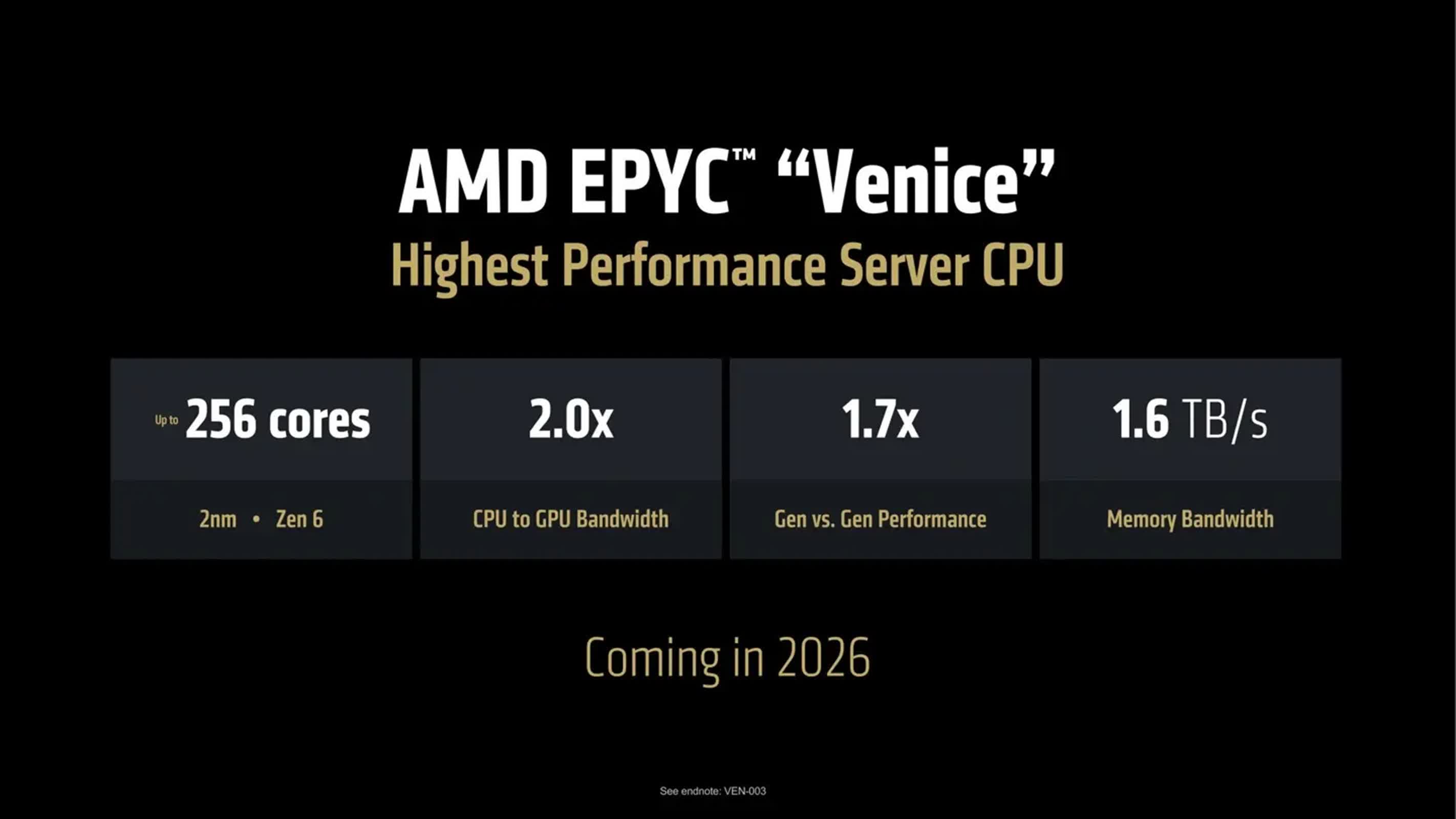

Venice makes a dramatic leap in processing power. The chip will support up to 256 Zen 6 cores, a 33 percent increase over the current Epyc Turin processors, which top out at 192 cores. AMD also claims that Venice will deliver up to 70 percent higher performance compared to its predecessor, an achievement that stems not just from more cores, but also from significant improvements in per-core efficiency and architectural enhancements.

The technological foundation for these gains is TSMC's advanced 2-nanometer manufacturing process. By skipping directly from 4nm to 2nm, AMD can pack more transistors into the same silicon area, boosting both performance and energy efficiency.

Memory bandwidth is another area where Venice stands out. The processor will more than double the per-socket memory bandwidth to 1.6 terabytes per second, up from 614 gigabytes per second in the current lineup. This is expected to be achieved through a combination of support for up to 16 channels of DDR5 memory and compatibility with advanced memory technologies such as MR-DIMM and MCR-DIMM. These improvements are critical for feeding data to the large number of high-performance cores, especially in data-intensive workloads common in AI and analytics.

AMD is also addressing the growing need for fast communication between CPUs and GPUs. Venice will double the bandwidth for CPU-to-GPU communication, likely by adopting PCI Express 6.0. With up to 128 PCIe lanes, the new platform will be able to move as much as 128 gigabytes of data per second in each direction, not counting encoding overhead. This is particularly important for AI training and inference, where rapid data movement between processors and accelerators is essential.

The Venice processor will debut on AMD's new SP7 platform, which is designed to accommodate the increased power and I/O demands of the chip. The SP7 socket is expected to support higher power delivery – potentially well beyond the 700 watts supported by the current SP5 platform – and allow for more compute complex dies on a single package. This new infrastructure will also enable more memory channels and greater expansion capabilities.

AMD plans to offer Venice in two main variants: a standard Zen 6 version with up to 96 cores and a high-density Zen 6c version, scaling up to the full 256 cores, both of which support up to 512 threads.

Looking ahead, Venice will anchor AMD's Helios rack-scale architecture, which will integrate the new CPUs with next-generation Instinct MI400 GPUs and advanced networking solutions. This system is expected to deliver a substantial leap in AI performance and memory capacity, setting the stage for even more powerful platforms in the years to follow.

English (US) ·

English (US) ·